МИНИСТЕРСТВО образования и науки Российской Федерации

ФЕДЕРАЛЬНОЕ Государственное БЮДЖЕТНОЕ образовательное учреждение

высшего профессионального образования

тюменский государственный нефтегазовый университет

институт кибернетики, информатики и связи

КУРСОВАЯ РАБОТА

Построение внутренней памяти процессорной системы

по дисциплине: «Вычислительная техника»

Техническое задание

Вариант – 6

Построить внутреннюю память процессорной системы, состоящую из ПЗУ и статического ОЗУ.

Разрядность ША – 20 , ШД – 8 .

Адреса, покрываемые ПЗУ - 00000-03FFF

Адреса, покрываемые ОЗУ – 80000-9FFFF

Емкость микросхемы ПЗУ - 16K*8

Емкость микросхемы ОЗУ - 64K*4

Введение……………………………………………………………………4

1 Теоритическая часть

1.1 Общая структура МПС…………………………………………………5

1.2 Подсистема памяти МПС………………………………………………7

1.3 Устройства памяти……………………………………………………...9

1.4 Статические ОЗУ. Принципы построения…………………………...11

1.5 Принцип записи/чтения информации………………………………...13

1.6 Построение пространства памяти заданного объема………………..14

2 Практическая часть

2.1 Определение емкости ПЗУ и ОЗУ...…………………………………16

2.2 Структура ПЗУ и ОЗУ……………………………………………........19

2.3 Общая структура памяти……………………………………………...20

Заключение…………………………….……………………………………21

Список литературы…………………………………………………………22

Введение

Информация, циркулирующая в вычислительной системе, хранится в памяти. Основными критериями оценки запоминающего устройства являются показатели емкости, быстродействия и потребляемой мощности.

Компьютерная память обеспечивает поддержку одной из наиважнейшей функций современного компьютера – способность длительного хранения информации.

В зависимости от места нахождения в вычислительной системе память подразделяют на внутреннюю (оперативную, сверхоперативную и постоянную) и внешнюю (различные накопители).

В теоретической части данной работы рассмотрена компьютерная память, ее виды и классификации, в практической части – осуществлено построение внутренней памяти процессорной системы.

В конце работы сделано заключение и приведен список использованной литературы.

1.1 Общая структура МПС

Микропроцессор (МП) – центральная часть любой микропроцессорной системы (МПС) – включает в себя арифметико-логическое устройство (АЛУ) и центральное управляющее устройство (ЦУУ), реализующее командный цикл. МП может функционировать только в составе МПС, включающей в себя, кроме МП, память, устройства ввода/вывода, вспомогательные схемы (тактовый генератор, контроллеры прерываний и прямого доступа к памяти (ПДП), шинные формирователи, регистры-защелки и др.

В любой МПС можно выделить следующие основные части (подсистемы):

внешние устройства (внешние ЗУ + устройства ввода/вывода);

подсистему прерываний;

подсистему прямого доступа в память.

процессорный модуль;

Рисунок 1 – Структура МПС с интерфейсом "Общая шина"

Связь между процессором и другими устройствами МПС может осуществляться по принципам радиальных связей, общей шины или комбинированным способом. В однопроцессорных МПС, особенно 8- и 16-разрядных, наибольшее распространение получил принцип связи "Общая шина", при котором все устройства подключаются к интерфейсу одинаковым образом (Рисунок 1).

Все сигналы интерфейса делятся на три основные группы – данных, адреса и управления. Многочисленные разновидности интерфейсов "Общая шина" обеспечивают передачу по раздельным или мультиплексированным линиям (шинам). Например, интерфейс Microbus, с которым работают большинство 8-разрядных МПС на базе i8080, передает адрес и данные по раздельным шинам, но некоторые управляющие сигналы передаются по шине данных. Интерфейс Q-bus, используемый в микро-ЭВМ фирмы DEC (отечественный аналог – микропроцессоры серии К1801) имеет мультиплексированную шину адреса/данных, по которой эта информация передается с разделением во времени. Естественно, что при наличии мультиплексированной шины в состав линий управления необходимо включать специальный сигнал, идентифицирующий тип информации на шине.

Обмен информацией по интерфейсу производится между двумя устройствами, одно из которых является активным, а другое – пассивным. Активное устройство формирует адреса пассивных устройств и управляющие сигналы. Активным устройством выступает, как правило, процессор, а пассивным – всегда память и некоторые ВУ. Однако иногда быстродействующие ВУ могут выступать в качестве задатчика (активного устройства) на интерфейсе, управляя обменом с памятью.

Концепция "Общей шины" предполагает, что обращения ко всем устройствам МПС производится в едином адресном пространстве, однако, в целях расширения числа адресуемых объектов, в некоторых системах искусственно разделяют адресные пространства памяти и ВУ, а иногда даже и памяти программ и памяти данных.

12 Подсистема памяти МПС

Распределение адресного пространства.

Объем адресного пространства МПС с интерфейсом "Общая шина" определяется главным образом разрядностью шины адреса и, кроме того, номенклатурой управляющих сигналов интерфейса. Управляющие сигналы могут определять тип объекта, к которому производится обращение (ОЗУ, ВУ, стек, специализированные ПЗУ и др.). В случае если МП не выдает сигналов, идентифицирующих пассивное устройство (или они не используются в МПС), – для селекции используются только адресные линии. Число адресуемых объектов составляет в этом случае 2 k , где k - разрядность шины адреса. Будем называть такое адресное пространство "единым". Иногда говорят, что ВУ в едином адресном пространстве "отображены на память", т.е. адреса ВУ занимают адреса ячеек памяти. Пример организации селекции устройств в едином адресном пространстве МПС на базе i8080 и распределение адресного пространства показаны на рисунке 2 и рисунке 3 соответственно.

Рисунок 2 – Структура единого адресного пространства

Рисунок 3 – Пример распределения единого адресного пространства

При небольших объемах памяти в МПС целесообразно использовать некоторые адресные линии непосредственно в качестве селектирующих (Рисунок 4), что позволяет уменьшить объем оборудования МПС за счет исключения селектора адреса. При этом, однако, адресное пространство используется крайне неэффективно.

При использовании информации о типе устройства, к которому идет обращение, можно одни и те же адреса назначать для разных устройств, осуществляя селекцию с помощью управляющих сигналов.

Так, большинство МП выдают в той или иной форме информацию о типе обращения. В результате в большинстве интерфейсов присутствуют отдельные управляющие линии для обращения к памяти и вводу/ выводу, реже - стеку или специализированному ПЗУ. В результате суммарный объем адресного пространства МПС может превышать величину 2 k .

Рисунок 4 – Использование адресных линий для прямой селекции устройств

1.3 Устройства памяти

Устройства памяти микропроцессорной системы (МПС) могут быть внешними (винчестер, дисковод, CD-ROM и т.д.) и внутренними (ОЗУ, ПЗУ).

В данной курсовой работе рассматривается внутренняя память МПС, которая может быть:

постоянной (ROM) или ПЗУ,

оперативной (RAM) или ОЗУ.

В свою очередь ПЗУ по способу записи/перезаписи информации различаются следующим образом.

ПЗУ – постоянные запоминающие устройства, в основу которых положены диодные матрицы. Матрицы прожигаются на заводе-изготовителе, пользователь ничего изменить не может (рисунок 5). При подаче U > U доп диод сгорает, остается перемычка; при сгоревшем диоде U узла = 0; при функционирующем диоде U узла = 1

ППЗУ – перепрограммируемые ПЗУ (матрицы поставляются пользователю с уровнем 1 во всех узлах, пользователь может только один раз прожечь матрицу по своей программе).

РПЗУ – репрограммируемые (т.е. многократно программируемые) ПЗУ.

Рисунок 5 – Элемент диодной матрицы.

По способу стирания информации РПЗУ могут быть: ультрафиолетовыми и электрическими.

Оперативные запоминающие устройства ОЗУ могут быть: динамическими (DRAM) и статическими (SRAM).

В динамических ОЗУ, построенных на МОП-транзисторных ячейках с дополнительной емкостью, информация после считывания пропадает, поэтому требуется ее регенерация (восстановление), а значит, такие ОЗУ при своей очевидной дешевизне имеют низкое быстродействие.

Статические ОЗУ, построенные на триггерных ячейках, хранят информацию после считывания и регенерации не требуют, имеют высокое быстродействие, хотя и существенно дороже динамических ОЗУ.

Современные схемы ОЗУ сочетают в себе обе технологии (SDRAM).

1.4 Статические ОЗУ. Принципы построения

Рисунок 6 – Микросхема статической памяти

Шина адреса (рисунок 6) подключается к микросхеме памяти по N адресным входам: A 0 – A N –1 .

Шина данных подключается по входам/выходам D, количество которых зависит от того, сколько матриц размещено в кристалле.

CS – вход выборки кристалла, управляет подключением буфера данных к шине.

– вход запись/чтения, определяет подключение входного или выходного буфера данных к шине данных.

Рассмотрим принцип выбора ячейки памяти по адресу.

Входы адресной шины подключаются к дешифраторам (DC) строки и столбца матрицы. Предположим, что к микросхеме подключается четыре адресных линии (А 0 – А 3), причем линии А 0 , А 1 подаются на DC строки, а линии А 2 , А 3 – на DC столбца.

Рисунок 7– Выбор ячейки по адресу: а – триггера; б – элемента матрицы

Предположим, что на адресных входах указан адрес 9, т.е. 1001.

Таким образом, DC строки по А 0 =1, А 1 =0 установит 1 на выходе 1, а DC столбца по А 2 =0, А 3 =1 установит 1 на выходе 2.

Во всех узлах матрицы расположены триггеры. Вход синхронизации триггера и его выход на общую для данной матрицы линию данных подключаются, как показано на рисунке 7, а.

Очевидно, что функционировать будет только тот триггер, у которого на входы элемента И от DC строки и DC столбца попадут 1.

В нашем случае будет выбран элемент матрицы, обведенный в кружок (рисунок 7, б).

1.5 Принцип записи/чтения информации

Инициализируем элемент матрицы, подав адрес на адресные входы. Теперь покажем, как будет происходить процесс записи/чтения данных. Заметим, что каждая матрица имеет один общий провод данных, т.е. каждый разряд данных записан в своей матрице. Адресация таких матриц производится параллельно.

Рассмотрим обращение к одному разряду данных. Только при подаче на вход CS уровня 0 (рис. 8) на выходе управляющих схем буферов чтения и записи может появиться 1. Причем на выходе управления буфером записи 1 появится при 0 на входе , а на выходе управления буфером чтения – при 1 на .

Рисунок 8 – Функции входов CS и

1.6 Построение пространства памяти заданного объема

Из микросхем SRAM небольшой емкости можно составить память любого заданного объема. Предположим, что в нашем распоряжении есть микросхемы SRAM емкостью 256×4. Необходимо составить память устройства емкостью 1 Кбайт или 1К×8. Схема 256×4 имеет 4 матрицы по 256 ячеек (256 = 2 8), т.е. схема имеет 8 адресных входов.

Рисунок 9 – Микросхема памяти 256×4

Для того чтобы обеспечить чтение/запись байта информации, надо добавить еще 4 матрицы внешним соединением (т.е. объединить 2 микросхемы).

Получим эквивалентную схему, позволяющую хранить 256 байт информации.

Для построения памяти на 1 Кбайт необходимо 4 таких схемы:

1К = 2 10 ; 2 10 / 2 8 = 2 2 = 4.

Рисунок 10 – Получение эквивалентной схемы 256×8

Доступ к такой памяти осуществляется по 10 адресным линиям (1К = 2 10): непосредственно к схеме подключаются 8 адресных линий, а 2 – к дешифратору, с помощью которого выбирается одно из 4 направлений.

Общая схема памяти (рисунок 11) составлена из эквивалентных схем (рисунок 10), исходная микросхема представлена на рисунке 9.

Рисунок 11 – Схема оперативной статической памяти объемом 1Кбайт

2.1 Практическая часть

Построить внутреннюю память процессорной системы, состоящую из ПЗУ и статического ОЗУ. Процессорная система работает в реальном режиме.

Разрядность ША - 20, ШД - 8.

|

от 00000 до 03FFF |

от 80000 до 9FFFF |

Определение емкости ПЗУ и ОЗУ

По полученному диапазону адресов определим емкость ПЗУ и ОЗУ.

Определим количество изменяющихся разрядов и запишем адрес в двоичном коде.

ПЗУ от 00000 до 03FFF

Начальный адрес: 00000000000000000000 2 .

Конечный адрес: 00000011111111111111 2 .

Изменились 14 разрядов, значит, емкость ПЗУ - 2 14 .

Для 8-разрядной шины данных емкость ПЗУ 2 14 *8:

2 14 = 2 10 *2 4 ,

2 10 = 1К - килобайт, таким образом, емкость ПЗУ равна 16К*8.

ОЗУ от 80000 до 9FFFF

Начальный адрес: 10000000000000000000 2 .

Конечный адрес: 10011111111111111111 2 .

Изменилось 17 разрядов.

Для 8-разрядной шины данных емкость ОЗУ равна:

2 17 = 2 10 *2 7

2 10 = 1К - килобайт, таким образом, емкость ОЗУ равна 128К*8.

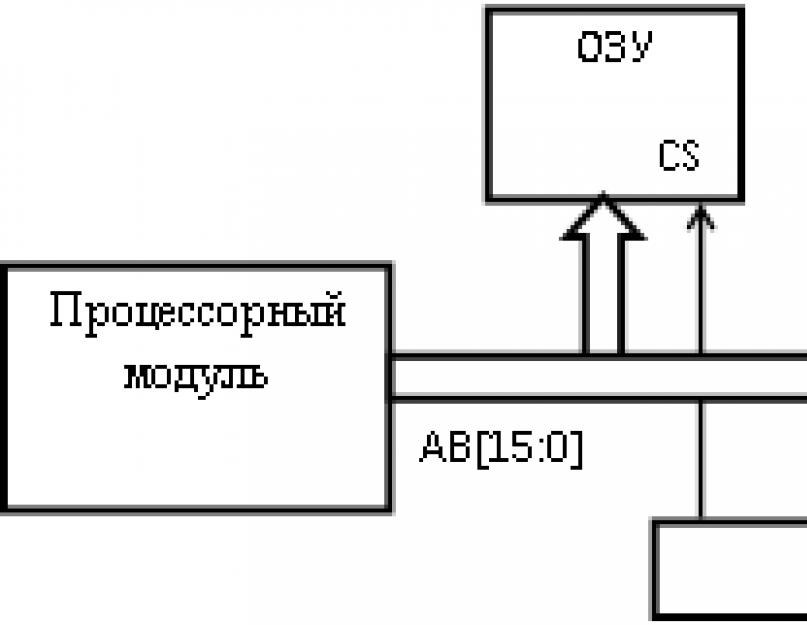

Для изображения схемы необходимо определить емкости микросхем ОЗУ и ПЗУ. ПЗУ имеет емкость 16К*8 (рис. 1), а ОЗУ - 64К*4 (рис. 2).Таким образом, схема ПЗУ имеет 14 адресных входов 16К = 2 14 , восемь вход/ выход данных и вход CS (выборки кристалла). Схема ОЗУ имеет 17 адресных входов 128К= 2 17 , четыре вход/выход данных, входы CS и

Рисунок 1 - Микросхема ПЗУ 16К*8

Рисунок 2 - Микросхема ОЗУ 64К*4

Структура ПЗУ

Емкость ПЗУ - 16К*8. Емкость микросхемы 16К*8, значит, для получения нужной емкости ПЗУ построить одну микросхему (рис. 3).

Рисунок3 - Структура ПЗУ 16К*8

Структура ОЗУ

Емкость ОЗУ 128К*8, емкость микросхемы 64К*4, значит, для построения такого ОЗУ необходимо построить 2 микросхемы.

Рисунок 4 - Структура ОЗУ 128К*8

Общая структура памяти

По заданию начальные адреса ПЗУ и ОЗУ следующие:

ПЗУ (00000 – 00000000000000000000 2),

ОЗУ (80000 –10000000000000000000 2).

По состоянию разрядов: А19, А18 - 00 работает ПЗУ, а по состоянию А19, А18 - 01 работает ОЗУ. С помощью простейшей логики можно

построить дешифратор направлений ПЗУ/ОЗУ (рис. 5).

Рисунок 5 - Дешифратор направлений ПЗУ-ОЗУ

Рисунок 6 - Общая структура проектируемой памяти

Заключение

В данной курсовой работе была осуществлена задача разработки блока внутренней памяти процессорной системы, состоящую из ПЗУ и статического ОЗУ. Были описаны в аналитическом, структурном и расчетно-графическом виде все необходимые узлы и элементы.

При расчете данной курсовой работы использовались математические и графические пакеты, такие как:

Список литературы

1 Угрюмов Е.П. Цифровая схемотехника. СПб: БХВ-СПб, 2000.

2 Большие интегральные микросхемы запоминающих устройств: справочник. М.: Радио и связь, 1990.

Память - это всегда очень сложная структура, включающая в себя множество элементов. Правда, внутренняя структура памяти - регулярная, большинство элементов одинаковые, связи между элементами сравнительно простые, поэтому функции, выполняемые микросхемами памяти, не слишком сложные.Память , как и следует из ее названия, предназначена для запоминания, хранения каких-то массивов информации, проще говоря, наборов, таблиц, групп цифровых кодов. Каждый код хранится в отдельном элементе памяти, называемом ячейкой памяти. Основная функция любой памяти как раз и состоит в выдаче этих кодов на выходы микросхемы по внешнему запросу. А основной параметр памяти - это ее объем, то есть количество кодов, которые могут в ней храниться, и разрядность этих кодов.

Для обозначения количества ячеек памяти используются следующие специальные единицы измерения:

- 1К - это 1024, то есть 2 10 (читается "кило-"" или "ка-"), примерно равно одной тысяче;

- 1М - это 1048576, то есть 2 20 (читается "мега-"), примерно равно одному миллиону;

- 1Г - это 1073741824, то есть 2 30 (читается "гига-"), примерно равно одному миллиарду.

Принцип организации памяти записывается следующим образом: сначала пишется количество ячеек, а затем через знак умножения (косой крест) - разрядность кода, хранящегося в одной ячейке. Например, организация памяти 64Кх8 означает, что память имеет 64К (то есть 65536) ячеек и каждая ячейка - восьмиразрядная. А организация памяти 4М х 1 означает, что память имеет 4М (то есть 4194304) ячеек, причем каждая ячейка имеет всего один разряд. Общий объем памяти измеряется в байтах (килобайтах - Кбайт, мегабайтах - Мбайт, гигабайтах - Гбайт) или в битах (килобитах - Кбит, мегабитах - Мбит, гигабитах - Гбит).

В зависимости от способа занесения (записи) информации и от способа ее хранения, микросхемы памяти разделяются на следующие основные типы:

- Постоянная память (ПЗУ - постоянное запоминающее устройство , ROM - Read Only Memory - память только для чтения), в которую информация заносится один раз на этапе изготовления микросхемы. Такая память называется еще масочным ПЗУ . Информация в памяти не пропадает при выключении ее питания, поэтому ее еще называют энергонезависимой памятью.

- Программируемая постоянная память (ППЗУ - программируемое ПЗУ , PROM - Programmable ROM), в которую информация может заноситься пользователем с помощью специальных методов (ограниченное число раз). Информация в ППЗУ тоже не пропадает при выключении ее питания, то есть она также энергонезависимая.

- Оперативная память (ОЗУ - оперативное запоминающее устройство , RAM - Random Access Memory - память с произвольным доступом), запись информации в которую наиболее проста и может производиться пользователем сколько угодно раз на протяжении всего срока службы микросхемы. Информация в памяти пропадает при выключении ее питания.

Существует множество промежуточных типов памяти, а также множество подтипов , но указанные - самые главные, принципиально отличающиеся друг от друга. Хотя, разница между ПЗУ и ППЗУ с точки зрения разработчика цифровых устройств, как правило, не так уж велика. Только в отдельных случаях, например, при использовании так называемой флэш-памяти (flash- memory ), представляющей собой ППЗУ с многократным электрическим стиранием и перезаписью информации, эта разница действительно чрезвычайно важна. Можно считать, что флэш-память занимает промежуточное положение между ОЗУ и ПЗУ .

В общем случае любая микросхема памяти имеет следующие информационные выводы (рис. 11.1):

Рис.

11.1.

- Адресные выводы (входные), образующие шину адреса памяти. Код на адресных линиях представляет собой двоичный номер ячейки памяти, к которой происходит обращение в данный момент. Количество адресных разрядов определяет количество ячеек памяти: при количестве адресных разрядов n количество ячеек памяти равно 2 n .

- Выводы данных (выходные), образующие шину данных памяти. Код на линиях данных представляет собой содержимое той ячейки памяти, к которой производится обращение в данный момент. Количество разрядов данных определяет количество разрядов всех ячеек памяти (обычно оно бывает равным 1, 4, 8, 16). Как правило, выходы данных имеют тип выходного каскада ОК или 3С.

- В случае оперативной памяти, помимо выходной шины данных , может быть еще и отдельная входная шина данных , на которую подается код, записываемый в выбранную ячейку памяти. Другой возможный вариант - совмещение входной и выходной шин данных, то есть двунаправленная шина, направление передачи информации по которой определяется управляющими сигналами. Двунаправленная шина применяется обычно при количестве разрядов шины данных 4 или более.

- Управляющие выводы (входные), которые определяют режим работы микросхемы. В большинстве случаев у памяти имеется вход выбора микросхемы CS (их может быть несколько, объединенных по функции И). У оперативной памяти также обязательно есть вход записи WR, активный уровень сигнала на котором переводит микросхему в режим записи.

Мы в данной лекции не будем, конечно, изучать все возможные разновидности микросхем памяти, для этого не хватит целой книги. К тому же эта информация содержится в многочисленных справочниках. Микросхемы памяти выпускаются десятками фирм во всем мире, поэтому даже перечислить все их не слишком просто, не говоря уже о том, чтобы подробно рассматривать их особенности и параметры. Мы всего лишь рассмотрим различные схемы включения типичных микросхем памяти для решения наиболее распространенных задач, а также методы проектирования некоторых узлов и устройств на основе микросхем памяти. Именно это имеет непосредственное отношение к цифровой схемотехнике. И именно способы включения микросхем мало зависят от характерных особенностей той или иной микросхемы той или иной фирмы.

В данном разделе мы не будем говорить о флэш-памяти, так как это отдельная большая тема. Мы ограничимся только простейшими микросхемами ПЗУ и ППЗУ, информация в которые заносится раз и навсегда (на этапе изготовления или же самим пользователем). Мы также не будем рассматривать здесь особенности оборудования для программирования ППЗУ (так называемых программаторов ), принципы их построения и использования, - это отдельная большая тема. Мы будем считать, что нужная нам информация может быть записана в ПЗУ или ППЗУ, а когда, как, каким способом она будет записана, нам не слишком важно. Все эти допущения позволят нам сосредоточиться именно на схемотехнике узлов и устройств на основе ПЗУ и ППЗУ (для простоты будем называть их в дальнейшем просто ПЗУ ).

Упомянем здесь только, что ППЗУ делятся на репрограммируемые или перепрограммируемые

Все виды памяти, которые мы рассматривали до сих пор, имеют одно общее свойство: в них можно и записывать информацию, и считывать ее. Такая память называется ОЗУ (оперативное запоминающее устройство). Существует два типа ОЗУ: статическое и динамическое. Статическое ОЗУ конструируется с использованием D-триггеров. Информация в ОЗУ сохраняется на протяжении всего времени, пока к нему подается питание: секунды, минуты, часы и даже дни. Статическое ОЗУ работает очень быстро. Обычно время доступа составляет несколько наносекунд. По этой причине статическое ОЗУ часто используется в качестве кэш-памяти второго уровня.

В динамическом ОЗУ, напротив, триггеры не используются. Динамическое ОЗУ представляет собой массив ячеек, каждая из которых содержит транзистор и крошечный конденсатор. Конденсаторы могут быть заряженными и разряженными, что позволяет хранить нули и единицы. Поскольку электрический заряд имеет тенденцию исчезать, каждый бит в динамическом ОЗУ должен обновляться (перезаряжаться) каждые несколько миллисекунд, чтобы предотвратить утечку данных. Поскольку об обновлении должна заботиться внешняя логика, динамическое ОЗУ требует более сложного сопряжения, чем статическое, хотя этот недостаток компенсируется большим объемом.

Поскольку динамическому ОЗУ нужен только 1 транзистор и 1 конденсатор на бит (статическому ОЗУ требуется в лучшем случае б транзисторов на бит), динамическое ОЗУ имеет очень высокую плотность записи (много битов на одну микросхему). По этой причине основная память почти всегда строится на основе динамических ОЗУ. Однако динамические ОЗУ работают очень медленно (время доступа занимает десятки наносекунд). Таким образом, сочетание кэш-памяти на основе статического ОЗУ и основной памяти на основе динамического ОЗУ соединяет в себе преимущества обоих устройств.

Существует несколько типов динамических ОЗУ. Самый древний тип, который все еще используется, - FPM (Fast Page Mode - быстрый постраничный

Память 175

режим)-. Это ОЗУ представляет собой матрицу битов. Аппаратное обеспечение представляет адрес строки, а затем - адреса столбцов (мы описывали этот процесс, когда говорили об устройстве памяти, показанном на рис. 3.30, 6).

FPM постепенно замещается EDO 1 (Extended Data Output - память с расширенными возможностями вывода), которая позволяет обращаться к памяти еще до того, как закончилось предыдущее обращение. Такой конвейерный режим не ускоряет доступ к памяти, но зато увеличивает пропускную способность, выдавая больше слов в секунду.

И FPM, и EDO являются асинхронными. В отличие от них так называемое синхронное динамическое ОЗУ управляется одним синхронизирующим сигналом. Данное устройство представляет собой гибрид статического и динамического ОЗУ. Синхронное динамическое ОЗУ часто используется при производстве кэш-памяти большого объема. Возможно, данная технология в будущем станет наиболее предпочтительной и в изготовлении основной памяти.

ОЗУ - не единственный тип микросхем памяти. Во многих случаях данные должны сохраняться, даже если питание отключено (например, если речь идет об игрушках, различных приборах и машинах). Более того, после установки ни программы, ни данные не должны изменяться. Эти требования привели к появлению ПЗУ (постоянных запоминающих устройств), которые не позволяют изменять и стирать хранящуюся в них информацию (ни умышленно, ни случайно). Данные записываются в ПЗУ в процессе производства. Для этого изготавливается трафарет с определенным набором битов, который накладывается на фоточувствительный материал, а затем открытые (или закрытые) части поверхности вытравливаются. Единственный способ изменить программу в ПЗУ - поменять целую микросхему.

ПЗУ стоят гораздо дешевле ОЗУ, если заказывать их большими партиями, чтобы оплатить расходы на изготовление трафарета. Однако они не допускают изменений после выпуска с производства, а между подачей заказа на ПЗУ и его выполнением может пройти несколько недель. Чтобы компаниям было проще разрабатывать новые устройства, основанные на ПЗУ, были выпущены программируемые ПЗУ. В отличие от обычных ПЗУ, их можно программировать в условиях эксплуатации, что позволяет сократить время выполнения заказа. Многие программируемые ПЗУ содержат массив крошечных плавких перемычек. Можно пережечь определенную перемычку, если выбрать нужную строку и нужный столбец, а затем приложить высокое напряжение к определенному выводу микросхемы.

Следующая разработка этой линии - стираемое программируемое ПЗУ, которое можно не только программировать в условиях эксплуатации, но и стирать с него информацию. Если кварцевое окно в данном ПЗУ подвергать воздействию сильного ультрафиолетового света в течение 15 минут, все биты установятся на 1. Если нужно сделать много изменений во время одного этапа проектирования, стираемые ПЗУ гораздо экономичнее, чем обычные программируемые ПЗУ, поскольку их можно использовать многократно. Стираемые программируемые ПЗУ обычно устроены так же, как статические ОЗУ. Например, микросхема 27С040 имеет структуру, которая показана на рис. 3.30, а, а такая структура типична для статического ОЗУ.

Динамическая намять типа EDO вытеснила обычную динамическую память, работающую н режиме FPM, в середине 90-х годов. - Примеч. научи, ред.

Следующий этап - электронно-перепрограммируемое ПЗУ, с которого можно стирать информацию, прилагая к нему импульсы, и которое не нужно для этого помещать в специальную камеру, чтобы подвергнуть воздействию ультрафиолетовых лучей. Кроме того, чтобы перепрограммировать данное устройство, его не нужно вставлять в специальный аппарат для программирования, в отличие от стираемого программируемого ПЗУ. Но с другой стороны, самые большие электронно-перепрограммируемые ПЗУ в 64 раза меньше обычных стираемых ПЗУ, и работают они в два раза медленнее. Электронно-перепрограммируемые ПЗУ не могут конкурировать с динамическими и статическими ОЗУ, поскольку они работают в 10 раз медленнее, их емкость в 100 раз меньше и они стоят гораздо дороже. Они используются только в тех ситуациях, когда необходимо сохранение информации при выключении питания.

Более современный тип электронно-перепрограммируемого ПЗУ - флэш-память. В отличие от стираемого ПЗУ, которое стирается под воздействием ультрафиолетовых лучей, и от электронно-программируемого ПЗУ, которое стирается по байтам, флэш-память стирается и записывается блоками. Как и любое электронно-перепрограммируемое ПЗУ, флэш-память можно стирать, не вынимая ее из микросхемы. Многие изготовители производят небольшие печатные платы, содержащие десятки мегабайтов флэш-памяти. Они используются для хранения изображений в цифровых камерах и для других целей. Возможно, когда-нибудь флэш-память вытеснит диски, что будет грандиозным шагом вперед, учитывая время доступа в 100 не. Основной технической проблемой в данный момент является то, что флэш-память изнашивается после 10 000 стираний, а диски могут служить годами независимо от того, сколько раз они перезаписывались. Краткое описание различных типов памяти дано в табл. 3.2.

Таблица 3.2. Характеристики различных видов памяти

| Тип запо- | Категория | Стирание | Изменение | Энерго- | Применение |

| минающего | записи | информации | зависи- | ||

| устройства | по байтам | мость | |||

| Статическое | Чтение/ | Электрическое | Да | Да | Кэш-память |

| ОЗУ (SRAM) | запись | второго уровня | |||

| Динамическое | Чтение/ | Электрическое | Да | Да | Основная память |

| ОЗУ (DRAM) | запись | ||||

| ПЗУ(ЯОМ) | Только | Невозможно | Нет | Нет | Устройства |

| чтение | большого размера | ||||

| Програм- | Только | Невозможно | Нет | Нет | Устройства |

| мируемое | чтение | небольшого | |||

| ПЗУ (PROM) | размера | ||||

| Стираемое | Преиму- | Ультра- | Нет | Нет | Моделирование |

| програм- | щественно | фиолетовый | устройств | ||

| мируемое | чтение | свет | |||

| ПЗУ(ЕРРЮМ) | |||||

| Электронно- | Преиму- | Электрическое | Да | Нет | Моделирование |

| перепрограм- | щественно | устройств | |||

| мируемое ПЗУ | чтение | ||||

| (EEPROM) | |||||

| флэш-память | Чтение/ | Электрическое | Нет | Нет | Цифровые камеры |

| (Flash) | запись |

Микросхемы процессоров и шины 177

Микросхемы процессоров и шины

Поскольку нам уже известна некоторая информация о МИС, СИС и микросхемах памяти, то мы можем сложить все составные части вместе и изучать целые системы. В этом разделе сначала мы рассмотрим процессоры на цифровом логическом уровне, включая цоколевку (то есть значение сигналов на различных выводах). Поскольку центральные процессоры тесно связаны с шинами, которые они используют, мы также кратко изложим основные принципы разработки шин. Б следующих разделах мы подробно опишем примеры центральных процессоров и шин для них.

Микросхемы процессоров

Все современные процессоры помещаются на одной микросхеме. Это делает вполне определенным их взаимодействие с остальными частями системы. Каждая микросхема процессора содержит набор выводов, через которые происходит обмен информацией с внешним миром. Одни выводы передают сигналы от центрального процессора, другие принимают сигналы от других компонентов, третьи делают и то и другое. Изучив функции всех выводов, мы сможем узнать, как процессор взаимодействует с памятью и устройствами ввода-вывода на цифровом логическом уровне.

Выводы микросхемы центрального процессора можно подразделить на три типа: адресные, информационные и управляющие. Эти выводы связаны с соответствующими выводами на микросхемах памяти и микросхемах устройств ввода-вывода через набор параллельных проводов (так называемую шину). Чтобы вызвать команду, центральный процессор сначала посылает в память адрес этой команды по адресным выводам. Затем он запускает одну или несколько линий управления, чтобы сообщить памяти, что ему нужно, например, прочитать слово. Память выдает ответ, помещая требуемое слово на информационные выводы процессора и посылая сигнал о том, что это сделано. Когда центральный процессор получает данный сигнал, он принимает слово и выполняет вызванную команду. ■ Команда может требовать чтения или записи слов, содержащих данные. В этом случае весь процесс повторяется для каждого дополнительного слова. Как происходит процесс чтения и записи, мы подробно рассмотрим ниже. Важно понимать, что центральный процессор обменивается информацией с памятью и устройствами ввода-вывода, подавая сигналы на выводы и принимая сигналы на входы. Другого способа обмена информацией не существует.

Число адресных выводов и число информационных выводов - два ключевых параметра, которые определяют производительность процессора. Микросхема, содержащая m адресных выводов, может обращаться к 2 т ячейкам памяти. Обычно m равно 16, 20, 32 или 64. Микросхема, содержащая п информационных выводов, может считывать или записывать n-битное слово за одну операцию. Обычно п равно 8, 16, 32, 36 или 64. Центральному процессору с 8 информационными выводами понадобится 4 операции, чтобы считать 32-битное слово, тогда как процессор, имеющий 32 информационных вывода, может сделать ту же работу в одну

Глава 3. Цифровой логический уровень

операцию. Следовательно, микросхема с 32 информационными выводами работает гораздо быстрее, но и стоит гораздо дороже.

Кроме адресных и информационных выводов каждый процессор содержит выводы управления. Выводы управления регулируют и синхронизируют поток данных к процессору и от него, а также выполняют другие разнообразные функции. Все процессоры содержат выводы для питания (обычно +3,3 В или +5 В), «земли» и синхронизирующего сигнала (меандра). Остальные выводы разнятся от процессора к процессору. Тем не менее выводы управления можно разделить на несколько основных категорий:

1. Управление шиной.

2. Прерывание.

3. Арбитраж шины.

4. Состояние.

5. Разное.

Ниже мы кратко опишем каждую из этих категорий. Когда мы будем рассматривать микросхемы Pentium II, UltraSPARC II и picojava II, мы дадим более подробную информацию. Схема типичного центрального процессора, в котором используются эти типы сигналов, изображена на рис. 3.31.

3.1.Микросхемы памяти

Преимущество памяти, изображенной на рис. 3.28, состоит в том, что подобная структура применима при разработке памяти большого объема. Мы нарисовали схему 4x3 (для 4 слов по 3 бита каждое). Чтобы расширить ее до размеров 4x8, нужно добавить еще 5 колонок триггеров по 4 триггера в каждой, а также 5 входных и 5 выходных линий. Чтобы перейти от размера 4x3 к размеру 8x3, мы должны добавить еще четыре ряда триггеров по три триггера в каждом, а также адресную линию А2. При такой структуре число слов в памяти должно быть степенью двойки для максимальной эффективности, а число битов в слове может быть любым. Поскольку технология изготовления интегральных схем хорошо подходит для

производства микросхем с внутренней структурой повторяемой плоской поверхности, микросхемы памяти являются идеальным применением для этого. С развитием технологии число битов, которое можно вместить в одной микросхеме, постоянно увеличивается, обычно в два раза каждые 18 месяцев (закон Мура). С появлением больших микросхем маленькие микросхемы не всегда устаревают из-за компромиссов между преимуществами емкости, скорости, мощности, цены и сопряжения. Обычно самые большие современные микросхемы пользуются огромным спросом и, следовательно, стоят гораздо дороже за 1 бит, чем микросхемы небольшого размера.

При любом объеме памяти существует несколько различных способов орга-

низации микросхемы. На рис. 3.30 показаны две возможные структуры микросхемы в 4 Мбит: 512 Кх8 и 4096 Kxl. (Размеры микросхем памяти обычно даются в битах, а не в байтах, поэтому здесь мы будем придерживаться этого соглашения.) На рис. 3.30, а можно видеть 19 адресных линий для обращения к одному из 219 байтов и 8 линий данных для загрузки или хранения выбранного байта.

Сделаем небольшое замечание по поводу терминологии. На одних выводах

высокое напряжение вызывает какое-либо действие, на других - низкое напряжение. Чтобы избежать путаницы, мы будем употреблять термин «установить сигнал»,когда вызывается какое-то действие, вместо того чтобы говорить, что напряжение повышается или понижается. Таким образом, для одних выводов установка сигнала значит установку на 1, а для других - установку на 0. Названия выводов, которые устанавливаются на 0, содержат сверху черту. Сигнал CS устанавливается на 1, а сигнал CS - на 0. Противоположный термин - «сбросить».

А теперь вернемся к нашей микросхеме. Поскольку обычно компьютер содержит много микросхем памяти, нужен сигнал для выбора необходимой микросхемы, такой, чтобы нужная нам микросхема реагировала на вызов, а остальные нет.

Сигнал CS (Chip Select - выбор элемента памяти) используется именно для этой цели. Он устанавливается, чтобы запустить микросхему. Кроме того, нужен способ отличия считывания от записи. Сигнал WE (Write Enable - разрешение записи) используется для указания того, что данные должны записываться, а не считываться. Наконец, сигнал (Ж (Output Enable - разрешение выдачи выходных сигналов) устанавливается для выдачи выходных сигналов. Когда этого сигнала нет, выход отсоединен от остальной части схемы. На рис. 3.30, б используется другая схема адресации. Микросхема представляет собой матрицу 2048x2048 однобитных ячеек, что составляет 4 Мбит. Чтобы обратиться к микросхеме, сначала нужно выбрать строку. Для этого И-битный номер этой строки подается на адресные выводы. Затем устанавливается сигнал RAS (Row Address Strobe - строб адреса строки). После этого на адресные выводы подается номер столбца и устанавливается сигнал CAS (Column Address Strobe - строб адреса столбца). Микросхема реагирует на сигнал, принимая или выдавая 1 бит данных.

Большие микросхемы памяти часто производятся в виде матриц mxn, обращение к которым происходит по строке и столбцу. Такая организация памяти сокращает число необходимых выводов, но, с другой стороны, замедляет обращение к микросхеме, поскольку требуется два цикла адресации: один для строки, а другой для столбца. Чтобы ускорить этот процесс, в некоторых микросхемах можно вызывать адрес ряда, а затем несколько адресов столбцов для доступа к последовательным битам ряда.

Много лет назад самые большие микросхемы памяти обычно были устроены

так, как показано на рис. 3.30, б. Поскольку слова выросли от 8 до 32 битов и выше, использовать подобные микросхемы стало неудобно. Чтобы из микросхем 4096 Kxl построить память с 32-битными словами, требуется 32 микросхемы, работающие параллельно. Эти 32 микросхемы имеют общий объем, по крайней мере, 16 Мбайт. Если использовать микросхемы 512 Кх8, то потребуется всего 4 микросхемы, но при этом объем памяти будет составлять 2 Мбайт. Чтобы избежать наличия 32 микросхем, большинство производителей выпускают семейства микросхем с длиной слов 1,4, 8 и 16 битов.

3.2.ОЗУ и ПЗУ

Все виды памяти, которые мы рассматривали до сих пор, имеют одно общее свойство: в них можно и записывать информацию, и считывать ее. Такая память называется ОЗУ (оперативное запоминающее устройство). Существует два типа ОЗУ: статическое и динамическое. Статическое ОЗУ конструируется с использованием D-триггеров. Информация в ОЗУ сохраняется на протяжении всего времени, пока к нему подается питание: секунды, минуты, часы и даже дни. Статическое ОЗУ работает очень быстро. Обычно время доступа составляет несколько наносекунд. По этой причине статическое ОЗУ часто используется в качестве кэш-памяти второго уровня.

В динамическом ОЗУ, напротив, триггеры не используются. Динамическое

ОЗУ представляет собой массив ячеек, каждая из которых содержит транзистор и крошечный конденсатор. Конденсаторы могут быть заряженными и разряженными, что позволяет хранить нули и единицы. Поскольку электрический заряд имеет тенденцию исчезать, каждый бит в динамическом ОЗУ должен обновляться (перезаряжаться) каждые несколько миллисекунд, чтобы предотвратить утечку данных. Поскольку об обновлении должна заботиться внешняя логика, динамическое ОЗУ требует более сложного сопряжения, чем статическое, хотя этот недостаток компенсируется большим объемом.

Поскольку динамическому ОЗУ нужен только 1 транзистор и 1 конденсатор на бит (статическому ОЗУ требуется в лучшем случае 6 транзисторов на бит), динамическое ОЗУ имеет очень высокую плотность записи (много битов на одну микросхему). По этой причине основная память почти всегда строится на основе динамических ОЗУ. Однако динамические ОЗУ работают очень медленно (время доступа занимает десятки наносекунд). Таким образом, сочетание кэш-памяти на основе статического ОЗУ и основной памяти на основе динамического ОЗУ соединяет в себе преимущества обоих устройств.

Существует несколько типов динамических ОЗУ. Самый древний тип, кото-

рый все еще используется, - FPM (Fast Page Mode - быстрый постраничный режим). Это ОЗУ представляет собой матрицу битов. Аппаратное обеспечение представляет адрес строки, а затем - адреса столбцов (мы описывали этот процесс, когда говорили об устройстве памяти, показанном на рис. 3.30, 6).

FPM постепенно замещается EDO1 (Extended Data Output - память с расши-

ренными возможностями вывода), которая позволяет обращаться к памяти еще до того, как закончилось предыдущее обращение. Такой конвейерный режим не ускоряет доступ к памяти, но зато увеличивает пропускную способность, выдавая больше слов в секунду. И FPM, и EDO являются асинхронными. В отличие от них так называемое синхронное динамическое ОЗУ управляется одним синхронизирующим сигналом. Данное устройство представляет собой гибрид статического и динамического ОЗУ. Синхронное динамическое ОЗУ часто используется при производстве кэш-памяти большого объема. Возможно, данная технология в будущем станет наиболее

предпочтительной и в изготовлении основной памяти.

ОЗУ - не единственный тип микросхем памяти. Во многих случаях данные

должны сохраняться, даже если питание отключено (например, если речь идет об игрушках, различных приборах и машинах). Более того, после установки ни программы, ни данные не должны изменяться. Эти требования привели к появлению ПЗУ (постоянных запоминающих устройств), которые не позволяют изменять и стирать хранящуюся в них информацию (ни умышленно, ни случайно). Данные записываются в ПЗУ в процессе производства. Для этого изготавливается трафарет с определенным набором битов, который накладывается на фоточувствительный материал, а затем открытые (или закрытые) части поверхности вытравливаются.

Единственный способ изменить программу в ПЗУ - поменять целую микросхему. ПЗУ стоят гораздо дешевле ОЗУ, если заказывать их большими партиями, чтобы оплатить расходы на изготовление трафарета. Однако они не допускают изменений после выпуска с производства, а между подачей заказа на ПЗУ и его выполнением может пройти несколько недель. Чтобы компаниям было проще разрабатывать новые устройства, основанные на ПЗУ, были выпущены программируемые ПЗУ. В отличие от обычных ПЗУ, их можно программировать в условиях эксплуатации, что позволяет сократить время выполнения заказа. Многие программируемые ПЗУ содержат массив крошечных плавких перемычек. Можно пережечь определенную перемычку, если выбрать нужную строку и нужный столбец, а затем приложить высокое напряжение к определенному выводу микросхемы.

Следующая разработка этой линии - стираемое программируемое ПЗУ, которое можно не только программировать в условиях эксплуатации, но и стирать с него информацию. Если кварцевое окно в данном ПЗУ подвергать воздействию сильного ультрафиолетового света в течение 15 минут, все биты установятся на 1.

Если нужно сделать много изменений во время одного этапа проектирования, стираемые ПЗУ гораздо экономичнее, чем обычные программируемые ПЗУ, поскольку их можно использовать многократно. Стираемые программируемые ПЗУ обычно устроены так же, как статические ОЗУ. Например, микросхема 27С040 имеет структуру, которая показана на рис. 3.30, а, а такая структура типична для статического ОЗУ.

Следующий этап - электронно-перепрограммируемое ПЗУ, с которого мож-

но стирать информацию, прилагая к нему импульсы, и которое не нужно для этого помещать в специальную камеру, чтобы подвергнуть воздействию ультрафиолетовых лучей. Кроме того, чтобы перепрограммировать данное устройство, его не нужно вставлять в специальный аппарат для программирования, в отличие от стираемого программируемого ПЗУ, Но с другой стороны, самые большие электронно-перепрограммируемые ПЗУ в 64 раза меньше обычных стираемых ПЗУ, и работают они в два раза медленнее. Электронно-перепрограммируемые ПЗУ не могут конкурировать с динамическими и статическими ОЗУ, поскольку они работают в 10 раз медленнее, их емкость в 100 раз меньше, и они стоят гораздо дороже. Они

используются только в тех ситуациях, когда необходимо сохранение информации при выключении питания.

Более современный тип электронно-перепрограммируемого ПЗУ - флэш-память. В отличие от стираемого ПЗУ, которое стирается под воздействием ультрафиолетовых лучей, и от электронно-программируемого ПЗУ, которое стирается по байтам, флэш-память стирается и записывается блоками. Как и любое электронно-перепрограммируемое ПЗУ, флэш-память можно стирать, не вынимая ее из микросхемы. Многие изготовители производят небольшие печатные платы, содержащие десятки мегабайтов флэш-памяти. Они используются для хранения изображений в цифровых камерах и для других целей. Возможно, когда-нибудь флэш-память вытеснит диски, что будет грандиозным шагом вперед, учитывая время доступа в 100 не. Основной технической проблемой в данный момент является то, что флэш-память изнашивается после 10 000 стираний, а диски могут служить годами независимо от того, сколько раз они перезаписывались. Краткое описание

различных типов памяти дано в табл. 3.2.

Лекция 8. Микросхемы управления и сопряжения.

1. Микросхемы процессора.

2. Шины и принципы их работы.

3. Средства сопряжения.

ПЗУ – память, информация в которой, будучи однажды записанной, изменению не подлежит. Например, программа загрузки в ОЗУ микропроцессорной системы информации из внешней памяти. Все типы ПЗУ используют один и тот же принцип построения схемы. Информация в ПЗУ представляется в виде наличия или отсутствия соединения между шинами адреса и данных.

Условное графическое обозначение ПЗУ представлено на рис.26.10.

Рис.26.10. Условное графическое обозначение ПЗУ

Рис. 26.11. Схема ПЗУ

На рис. 26.11 приведена схема простейшего ПЗУ. Для реализации ПЗУ достаточно использовать дешифратор, диоды, набор резисторов и шинные формирователи. Рассматриваемое ПЗУ содержит разрядных слова, т.е. его общий объем составляет 32 бит. Количество столбцов определяет разрядность слова, а количество строк – количество 8 разрядных слов. Диоды устанавливаются в тех местах, где должны храниться биты, имеющие значение логического «0» (дешифратор подает 0 на выбранную строку). В настоящее время вместо диодов ставят МОП-транзисторы.

В табл. 26.1 приведено состояние ПЗУ, схема которого приведена на рис. 26.11.

Таблица 26.1

Состояние простого ПЗУ

| Слово | Двоичное представление | ||||||||

| А0 | А1 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 |

Как правило, ПЗУ имеют многоразрядную организацию со структурой 2DM . Технологии изготовления самые разнообразные – КМОП, n-МОП, ТТЛ(Ш) и диодные матрицы.

Все ПЗУ можно разделить на следующие группы: программируемые при изготовлении (масочные), с однократным программированием и перепрограммируемые.

В запоминающих устройствах, программируемых при изготовлении (ПЗУ или ROM), информация записывается непосредственно в процессе их изготовления с помощью фотошаблона, называемого маской, на завершающем этапе технологического процесса. Такие ПЗУ называемые масочными, построены на диодах, биполярных или МОП транзисторах.

Область использования масочных ПЗУ – хранение стандартной информации, например знакогенераторы (коды букв латинского и русского алфавита), таблицы типовых функций (синусы, квадратичные функции), стандартное программное обеспечение.

Программируемые постоянные запоминающие устройства (ППЗУ, или PROM ) – ПЗУ с возможностью однократного электрического программирования. Этот вид памяти позволяет пользователю однократно запрограммировать микросхему памяти с помощью программаторов.

Микросхемы ППЗУ построены на запоминающих ячейках с плавкими перемычками. Процесс программирование заключается в избирательном пережигании плавких перемычек с помощью импульсов тока достаточной амплитуды и длительности. Плавкие перемычки включаются в электроды диодов или транзисторов.

На рис. 26.12 приведена схема ППЗУ с плавкими перемычками. Оно изготавливается со всеми диодами и перемычками, т.е. в матрице все «0», а при программировании пережигаются те перемычки, в ячейках которых должны быть логические «1».

Рис. 26.12. Фрагмент схемы ППЗУ

Репрограммируемые постоянные запоминающие устройства (РПЗУ и РПЗУ УФ) – ПЗУ с возможностью многократного электрического программирования. В ИС РПЗУ УФ (EPROM ) старая информация стирается с помощью ультрафиолетовых лучей, для чего в корпусе микросхемы имеется прозрачное окошко; в РПЗУ (EEPROM ) – с помощью электрических сигналов.

Запоминающие ячейки РПЗУ строятся на n -МОП или КМОП транзисторах. Для построения ЗЭ используются различные физические явления хранения заряда на границе между двумя диэлектрическими средами или проводящей и диэлектрической средой.

В первом варианте диэлектрик под затвором МОП транзистора делают из двух слоев: нитрида кремния и двуокиси кремния. Этот транзистор называется МНОП: металл – нитрид кремния – окисел – полупроводник. На границе диэлектрических слоев возникают центры захвата зарядов. Благодаря туннельному эффекту носители заряда могут проходить сквозь тонкую пленку окисла и скапливаться на границе раздела слоев. Этот заряд, являющийся носителем информации, хранимой МНОП-транзистором, приводит к изменению порогового напряжения транзистора. При этом пороговое напряжение возрастает настолько, что рабочее напряжение на затворе транзистора не в состоянии его открыть. Транзистор, в котором заряд отсутствует, легко открывается. Одно из состояний определено как логическая единица, второе – ноль.

Во втором варианте затвор МОП транзистора делают плавающим, т.е. не связанным с другими элементами схемы. Такой затвор заряжается током лавинной инжекции при подаче на сток транзистора высокого напряжения. В результате заряд на плавающем затворе влияет на ток стока, что используется при считывании информации, как и в предыдущем варианте с МНОП транзистором. Такие транзисторы получили название ЛИЗМОП (МОП транзистор с лавинной инжекцией заряда). Так как затвор транзистора окружен изолятором, ток утечки очень мал и информация может храниться достаточно долго (десятки лет).

В РПЗУ с электрическим стиранием над плавающим затвором транзистора размещают второй – управляющий затвор. Подача напряжения на него вызывает рассасывание заряда на плавающем затворе за счет туннельного эффекта. РПЗУ имеют весомые преимущества перед РПЗУ УФ, так как не требуют для перепрограммирования специальных источников ультрафиолетового света. ЗУ с электрическим стиранием практически вытеснили ЗУ с ультрафиолетовым стиранием.

Фрагмент схемы РПЗУ с использованием двухзатворных транзисторов типа ЛИЗМОП показан на рис. 26.13. Запись логического нуля осуществляется в режиме программирования с помощью заряда плавающего затвора. Стирание информации, т.е. разряд плавающего затвора, означает запись логической единицы. В этом случае при подаче сигнала по линии выборки опрашиваемые транзисторы открываются и передают напряжение U ПИТ на линии считывания.

Современные РПЗУ имеют информационную емкость до 4 Мбит при тактовой частоте до 80 МГц.

26.5. Flash -память

Основные принципы работы и тип запоминающих элементов Flash -памяти аналогичны ППЗУ с электрической записью и стиранием информации, построенной на транзисторах с плавающим затвором. Как правило, благодаря своим особенностям, Flash -память выделяют в отдельный класс. В ней производится стирание или всей записанной информации одновременно, или больших блоков информации, а не стирание отдельных слов. Это позволяет исключить схемы управления записью и стиранием отдельных байтов, что дает возможность значительно упростить схему ЗУ и достичь высокого уровня интеграции и быстродействия при снижении стоимости.

Рис.26.13. Фрагмент схемы РПЗУ

Современные тенденции развития электронных приборов требуют постоянного увеличения объема используемой памяти. На сегодня инженеру доступны микросхемы как энергозависимой памяти типа DRAM , которую характеризуют предельно низкая цена за бит и большие уровни интеграции, так и энергонезависимой Flash -памяти, себестоимость которой постоянно снижается и стремится к уровню DRAM .

Потребность в энергонезависимой Flash -памяти растет пропорционально степени продвижения компьютерных систем в сферу мобильных приложений. Надежность, малое энергопотребление, небольшие размеры и незначительный вес являются очевидными преимуществами носителей на основе Flash -памяти в сравнении с дисковыми накопителями. С учетом постоянного снижения стоимости хранения единицы информации в Flash -памяти, носители на её основе предоставляют все больше преимуществ и функциональных возможностей мобильным платформам и портативному оборудованию, использующему такую память. Среди многообразия типов памяти, Flash -память на основе ячеек NAND является наиболее подходящей основой для построения энергонезависимых устройств хранения больших объемов информации.

В настоящее время можно выделить две основных структуры построения флэш-памяти: память на основе ячеек NOR (ИЛИ-НЕ) и NAND (И-НЕ). Структура NOR (рис. 26.14, а) состоит из параллельно включенных элементарных ячеек хранения информации. Такая организация ячеек обеспечивает возможность произвольного доступа к данным и побайтной записи информации. В основе структуры NAND (рис. 26.14, б) лежит принцип последовательного соединения элементарных ячеек, образующих группы (в одной группе 16 ячеек), которые объединяются в страницы, а страницы – в блоки. При таком построении массива памяти обращение к отдельным ячейкам невозможно. Программирование выполняется одновременно только в пределах одной страницы, а при стирании обращение производится к блокам или к группам блоков.

Рис.26.14. Структуры на основе NOR (a) и NAND (б)

В результате различия в организации структуры между памятью NOR и NAND находят свое отражение в их характеристиках. При работе со сравнительно большими массивами данных процессы записи/стирания в памяти NAND выполняются значительно быстрее памяти NOR . Поскольку 16 прилегающих друг другу ячеек памяти NAND соединены последовательно друг с другом без каких-либо контактных промежутков, достигается высокая площадь размещения ячеек на кристалле, что позволяет получить большую емкость при одинаковых технологических нормах. В основе программирования флэш-памяти NAND лежит процесс туннелирования электронов. А поскольку он используется как для программирования, так и для стирания, достигается низкое энергопотребление микросхемы памяти. Последовательная структура организации ячеек позволяет получить высокую степень масштабируемости, что делает NAND-Flash лидером в гонке наращивания объемов памяти. Ввиду того, что туннелирование электронов осуществляется через всю площадь канала ячейки, интенсивность захвата заряда на единицу площади у NAND-Flash ниже, чем в других технологиях Flash -памяти, в результате чего она имеет более высокое количество циклов программирования/стирания. Программирование и чтение выполняются посекторно или постранично, блоками по 512 байт, для эмуляции общераспространенного размера сектора дисковых накопителей.

Более детально особенности микросхем Flash -памяти можно рассмотреть на примере кристаллов серии HY 27xx(08/16)1G 1M фирмы Hynix . На рис. 26.15 показана внутренняя структура и назначение выводов этих приборов.

Микросхема имеет следующие выводы:

I/O 8-15 – вход/выход данных для х16 устройств

I/O 0-7 – вход/выход данных, адресный вход или вход команд для х8 и х16 устройств;

ALE – включение адресной защелки;

CLE – включение защелки команд;

– выбор кристалла;

– разрешение чтения;

– чтение/занят (выход с открытым стоком);

– разрешение записи;

– защита от записи

V CC – напряжение питания;

V SS – общий вывод.

Рис.26.15. Схема внешних выводов (а), назначение выводов (б) и структурная схема (в) Flash -памяти

Линии адреса мультиплексированы с линиями ввода/вывода данных на 8-ми или 16-ти разрядной шине ввода/вывода. Такой интерфейс уменьшает количество используемых выводов и делает возможным переход к микросхемам большей емкости без изменения печатной платы. Каждый блок может быть запрограммирован и стерт 100000 раз. Микросхемы имеют выход «чтение/занят» с открытым стоком, который может использоваться для идентификации активности контроллера PER (Program/Erase/Read ). Поскольку выход сделан с открытым стоком, существует возможность подключать несколько таких выходов от разных микросхем памяти вместе через один «подтягивающий» резистор к положительному выводу источника питания.

Рис.26.16. Организация массива памяти NАND -структуры

Массив памяти NAND -структуры организован в виде блоков, каждый из которых содержит 32 страницы. Массив раздел на две области: главную и запасную (рис. 26.16).

Главная область массива используется для хранения данных, в то время как запасная область обычно задействована для хранения кодов коррекции ошибок (ECC ), программных флагов и идентификаторов негодных блоков (Bad Block ) основной области. В 8-битных устройствах страницы в главной области разделены на две полустраницы по 256 байт каждая, плюс 16 байт запасной области. В 16-ти битных устройствах страницы разделены на главную область объемом 256 слов и запасную объемом 8 слов.

Память на основе ячеек NOR имеет сравнительно большие времена стирания и записи, но обладает доступом к каждому биту на чтение. Данное обстоятельство позволяет применять такие микросхемы для записи и хранения программного кода, который не требует частого перезаписывания. Такими применениями могут быть, например, BIOS для встраиваемых компьютеров или ПО для телевизионных приставок.

Свойства NAND-Flash определили область ее применения: карты памяти и иные устройства хранения данных. Сейчас данный тип памяти применяется почти повсеместно в мобильных устройствах, фото- и видеокамерах и т.д. NAND-Flash лежит в основе практически всех типов карт памяти: SmartMedia , MMC , SecureDigital, MemoryStick

Достигнутая в настоящее время информационная емкость Flash -памяти достигает 8ГБит, типовая совокупная скорость программирования и стирания составляет до 33.6 мС / 64 кБ при тактовой частоте до 70 МГц.

Двумя основными направлениями эффективного использования Flash -памяти являются хранение редко изменяемых данных и замена памяти на магнитных дисках. Для первого направления используется Flash -память с адресным доступом, а для второго – файловая память.

26.6. ОЗУ типа FRAM

FRAM – оперативное энергонезависимое ЗУ, сочетающее высокое быстродействие и малую потребляемую мощность, присущие ОЗУ, со свойством хранения данных при отсутствии приложенного напряжения.

В сравнении с EEPROM и Flash -памятью время записи данных в ЗУ этого типа и потребляемая мощность намного меньше (менее 70 нс против нескольких миллисекунд), а ресурс по циклам записи намного выше (не менее 10 11 против 10 5 …10 6 циклов для EEPROM ).

FRAM должна стать в ближайшем будущем самой популярной памятью в цифровых устройствах. FRAM будет отличаться не только быстродействием на уровне DRAM , но и возможностью сохранять данные при отключении энергии. Словом, FRAM может вытеснить не только медленную Flash , но и обычную ОЗУ типа DRAM . Сегодня ферроэлектрическая память находит ограниченное применение, к примеру, в RFID -тэгах. Ведущие компании, в числе которых Ramtron, Samsung, NEC, Toshiba , активно развивают FRAM . Примерно к 2015 году на рынок должны поступить n -гигабайтные модули FRAM .

Указанные свойства FRAM обеспечивает сегнетоэлектрик (перовскит), используемый в качестве диэлектрика накопительного конденсатора ячейки памяти. При этом сегнетоэлектрическое ЗУ хранит данные не только в виде заряда конденсатора (как в традиционных ОЗУ), но и виде электрической поляризации кристаллической структуры сегнетоэлектрика. Сегнетоэлектрический кристалл имеет два состояния, которые могут соответствовать логическим 0 и 1.

Термин FRAM еще не устоялся. Первые FRAM получили название – ферродинамические ОЗУ. Однако в настоящее время в качестве запоминающих ячеек используется сегнетоэлектрик и сейчас FRAM часто называют сегнетоэлектрическим ОЗУ.

Первые FRAM имели 2Т /2С -архитектуру (рис.26.17, а), на основе которой выполняется и большинство современных микросхем сегнетоэлектрической памяти. Ячейка такого типа, в которой каждому биту соответствует индивидуальный опорный бит, позволяет определить разницу зарядов с высокой точностью. А благодаря считыванию дифференциального сигнала исключается влияние разброса параметров конденсаторов ячеек. Позже появились FRAM с архитектурой 1Т /1С (рис.26.17, б). Достоинство микросхем с такой архитектурой – меньшая, чем в обычных схемах площадь ячейки и, следовательно, меньшая стоимость микросхемы в пересчете на единицу информационной емкости.

На рис.26.18 приведена структурная схема сегнетоэлектрического ОЗУ (FRAM ) объемом 1 Мбит и параллельным интерфейсом доступа FM 20L 08 фирмы Ramtron . В таблице 26.1. показаны выводы микросхемы.

FM 20L 08 – энергонезависимая память с организацией 128К×8, которая считывается и записывается подобно стандартному статическому ОЗУ. Сохранность данных обеспечивается в течение 10 лет, при этом, нет необходимости задумываться о надежности хранения данных (неограниченная износостойкость), упрощается проектирование системы и исключается ряд недостатков альтернативного решения энергонезависимой памяти на основе статического ОЗУ с резервным батарейным питанием. Быстрота записи и неограниченное количество циклов перезаписи делают FRAM лидером по отношению к другим типам энергонезависимой памяти.

Рис.26.17. Ячейка памяти типа 2Т /2С (а) и 1Т /1С (б)

Рис.26.18. Структурная схема FRAM FM 20L 08